Protocol Analysis

Teledyne LeCroy's solution for Serial ATA testing is the SATracer/Trainer system. This all-in-one test platform offers traffic generation with integrated protocol analysis. The generator supports both Host and Device side emulation. It's a fully integrated system only slightly larger than a laptop which makes it suitable for both lab and field deployment.

SATracer provides everything needed for Serial ATA analysis including real-time hardware triggering and filtering on the critical components of Serial ATA traffic. Teledyne LeCroy's Expert Analysis software simplifies the overall debug process by using collapsible, color-coded packets to represent commands, FISs and primitives. This provides point-and-click "drill down" to lower level details along with the ease of use and understanding that Teledyne LeCroy is well known for.

SATA (Serial ATA) Overview

The storage industry is in the midst of a large-scale transition from parallel ATA, the dominant desktop storage interface, to Serial ATA. This migration reflects a broader transition across the industry to Serial technologies for computer-based communications. Driven primarily by lower voltages and costs required in future chipsets, Serial ATA is poised. For industry-wide adoption. The specification thoughtfully preserves software compatibility with the Parallel ATA command set. What's more, it offers smaller, thinner, lower cost cables that also offer compatibility at the physical layer with the emerging Serial Attached SCSI (SAS) standard.

Features

Performance - Parallel ATA does not have scalability to support several more speed doublings, and it is nearing its performance capacity. By contrast, Serial ATA defines a roadmap starting at 1.5 gigabits per second (equivalent to a data rate of 150 MB/s) and migrating to 3.0 gigabits per second (300 MB/s).

Lower Voltage - Parallel ATA's 5-volt signaling requirement will be increasingly difficult to meet as the industry continues to reduce chip core voltages. Serial ATA is better aligned with future manufacturing processes. It reduces signaling voltages to approximately 250 millivolts (1/4 volt).

Pin Count - Currently, the parallel ATA interface has 26 signal pins going into the interface chip. Serial ATA uses only 4 signal pins, improving the pin efficiency and accommodating a highly integrated chip implementation.

Improved Cabling - Parallel ATA bulky ribbon cables contain 40-pin header connector. Serial ATA introduces thin, flexible cabling scheme that offers longer cables and improved airflow within the chassis.

Software Compatible - Serial ATA is compatible at the register level with parallel ATA. This means Serial ATA requires no changes to existing software and operating systems in order to function, and it provides backward compatibility with existing operating environments.

SAS Compatibility - A significant feature offered by Serial ATA is the expectation that SATA will be form-factor compatibility with Serial Attached SCSI. SATA drives will plug directly into Serial Attached SCSI connectors and if supported in the system, will transparently operate as a SATA device. This allows systems to be deployed that can use either Serial Attached SCSI drives, for their high performance or SATA drives that will provide a lower-cost-per-megabyte storage platform.

Architecture

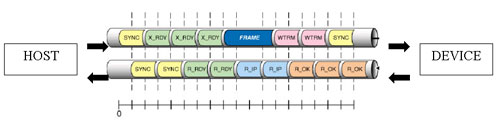

Serial ATA is a full duplex protocol. There is a continuous flow of signals from each device moving down the bus. The device and host are transmitting (TX) and receiving (RX) at the same time.

Bidirectional traffic pattern eliminates the need for bus negotiation overhead

Data characters vs Primitives - Primitives are the simplest elements within the Serial ATA protocol. Primitives are 32-bit DWORDs used to initiate control of the serial line functions (X_RDY, CONT, etc...). In addition to these "handshaking" and flow control signals, Primitives are also used to delimit or "frame" user data.

Frame Information Structure (FIS) - A frame is an indivisible unit of information exchanged between a host and device. A frame consists of a SOF primitive, a Frame Information Structure (FIS), a CRC calculated over the contents of the FIS, and an EOF primitive. A FIS is the user payload of a frame; a frame is a group of Dwords that convey information between host and device as described previously.

The figure above represents the logical structure of the Serial ATA hierarchy along with SATracer's representation of the protocol as viewed in the Teledyne LeCroy Trace™.

Links

Sources: Intel Development Labs; Serial ATA Specification 1.0 Copyright 2001; Serial ATA Working Group