Insight into the standard based on our real world testing experience

Instruction from experts with over 20 years of experience in storage

and networking

Fabric Architecture

UALink establishes a high-performance fabric designed specifically for

accelerator-to-accelerator communication. Its structured hierarchy of switches,

accelerators, nodes, and pods creates a scalable backbone that delivers massive

bandwidth with consistently low latency. The basic encoding of PAM4

- Nodes and Pods

- Accelerators and Switches

- Integration into datacenters

- Breakdown of components within a node

UPLI Interface

The UALink Protocol Level Interface defines how devices exchange data and control

information through structured Requests and Responses. This section explains how

UPLI organizes traffic and manages flow control.

- Originator vs Completer

- UPLI Channels and Beats

- Reads, Writes, and Atomic operations

- UPLI Flow Control

- Full transaction path

Manageability and Security

UALink introduces centralized management through the Pod Controller, which

supervises and coordinates up to 1024 accelerators within a single pod. Its

security framework, UALinkSec, protects traffic across the fabric and can

integrate with platforms that support Confidential Computing.

Transaction Layer

The UALink Transaction Layer is responsible for transforming UPLI beats into

64-byte TL Flits and reconstructing them on the receive side. It also manages

flow control and uses address caching to reduce overhead and improve efficiency

across the fabric.

- 64-byte TL Flit

- Address Caching

- Efficiency Examples

- Flow Control

Data Link

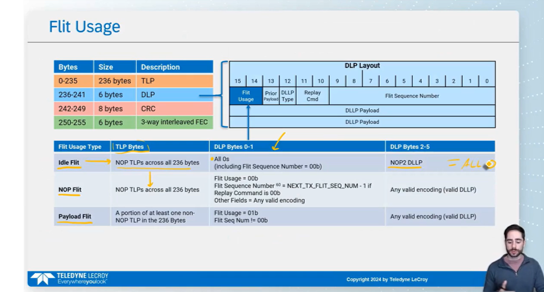

The Data Link Layer aggregates 64-byte TL Flits into 640-byte DL Flits for

transport across the physical layer. It also provides a lightweight messaging

service between link partners, enabling UART-style communication, pacing, and

replay mechanisms for reliable delivery.

- 640-byte DL Flit

- DL Message Service

- Flit Packing

- Link Level Replay

Physical Layer

The UALink Physical Layer builds on the 802.3 Ethernet PHY, supporting 1, 2, or 4

lanes at 212.5Gbps while adapting the encoding and FEC structures to align with

UALink’s 640-byte DL Flit format. This section highlights the PHY-level changes

that enable low-latency, high-reliability operation.

- RS and PCS Changes

- Low-Latency FEC Interleave

Reliability, Availability, and Serviceability (RAS)

This section explores how UALink’s RAS framework detects faults, isolates failing

components, and restores normal operation across accelerators and switches.